计算机组成原理

计算机组成原理

李阳有志者,事竟成,破釜沉舟,百二秦关终属楚;

苦心人,天不负,卧薪尝胆,三千越甲可吞吴;

一、计算机系统概述

(一)计算机系统层次结构

1.计算机系统的基本组成

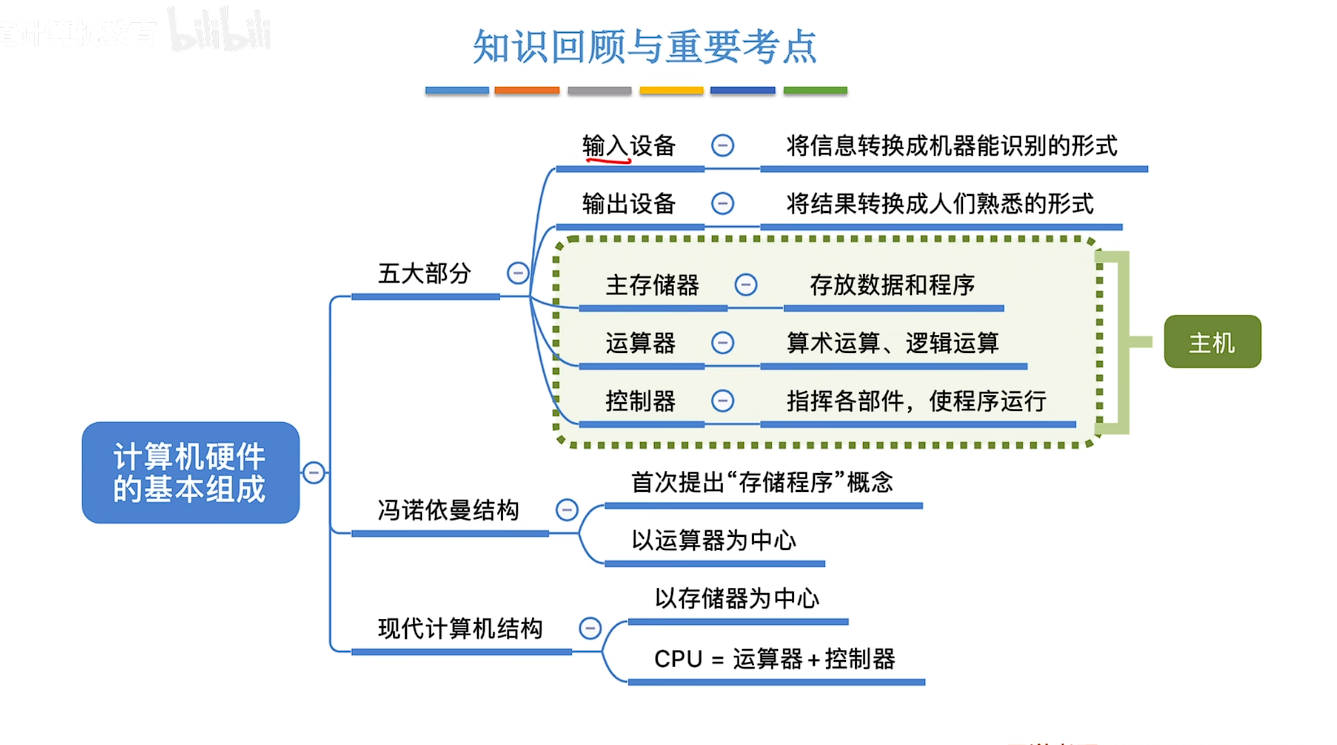

2.计算机硬件的基本组成

3.计算机软件和硬件的关系

4.计算机系统的工作原理

“存储程序”工作方式,

- 高级语言程序与机器语言程序之间的转换,

- 程序和指令的执行过程。

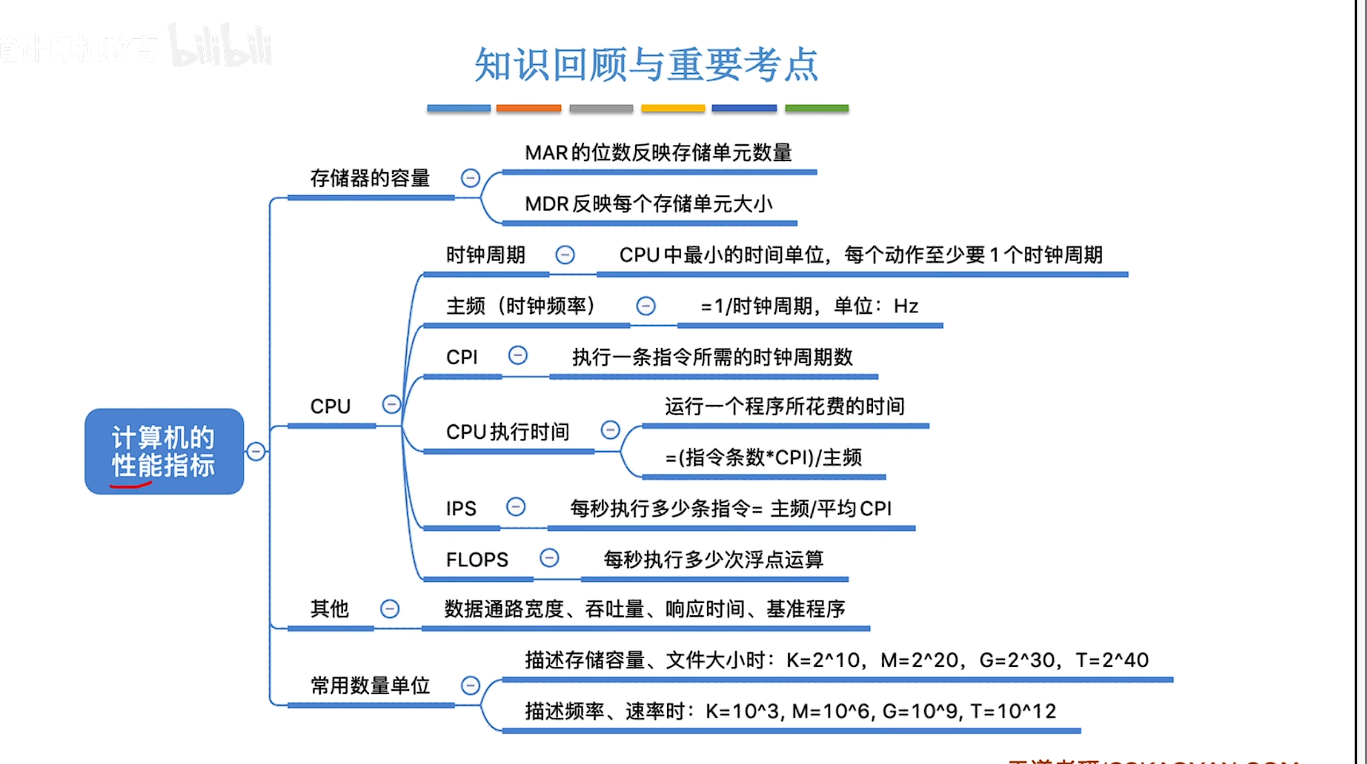

(二)计算机性能指标

- 吞吐最、响应时间;

- CPU 时钟周期、主频、CPI ,CPU执行时间

- MIPS, MFLOPS,GFLOPS、TFLOPS、PFLOPS、EFLOPS、ZFLOPS。;

一、计算机系统层次结构

1、计算机系统的组成

硬件系统和软件系统共同构成了一个完整的计算机系统,

硬件是指有形的网络设备,是计算机系统中实际物理装置的总称

软件是指硬盘上运行的程序相关的数据及文档

2、计算机硬件的基本组成

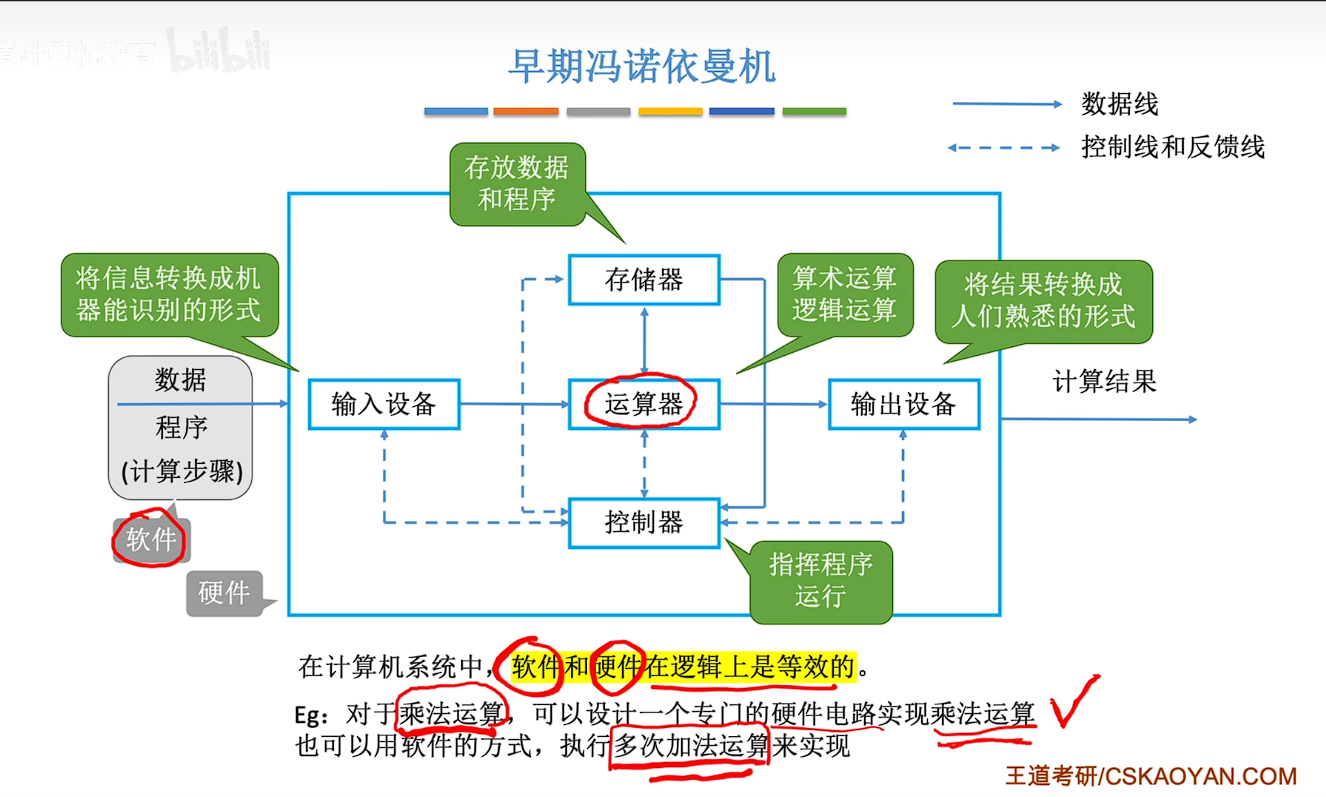

2.1 早期冯诺依曼机的结构

2.1.1 存储程序

“存储程序”的概念是指将指令以二进制代码的形式事先输入计算机的主存储器然后按其在存储器中的首地址执行程序的第一条指令,以后就按该程序的规定顺序执行其他指令,直至程序执行结束。

2.1.2 早期冯诺依曼机

2.1.2.1 冯·诺依曼计算机特点

- 计算机由五大部件组成

- 指令和数据以同等地位存于存储器,可按地址寻访

- 指令和数据用二进制表示

- 指令由操作码和地址码组成

- 存储程序

- 以运算器为中心

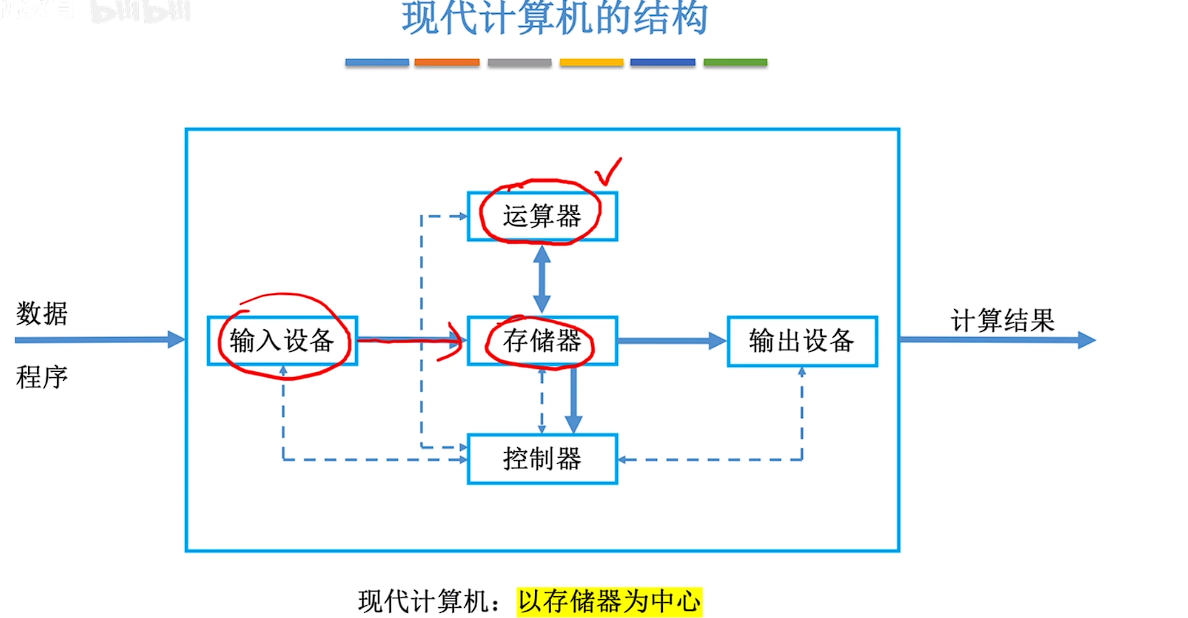

2.2 现代计算机的结构

CPU=运算器+控制器+寄存器

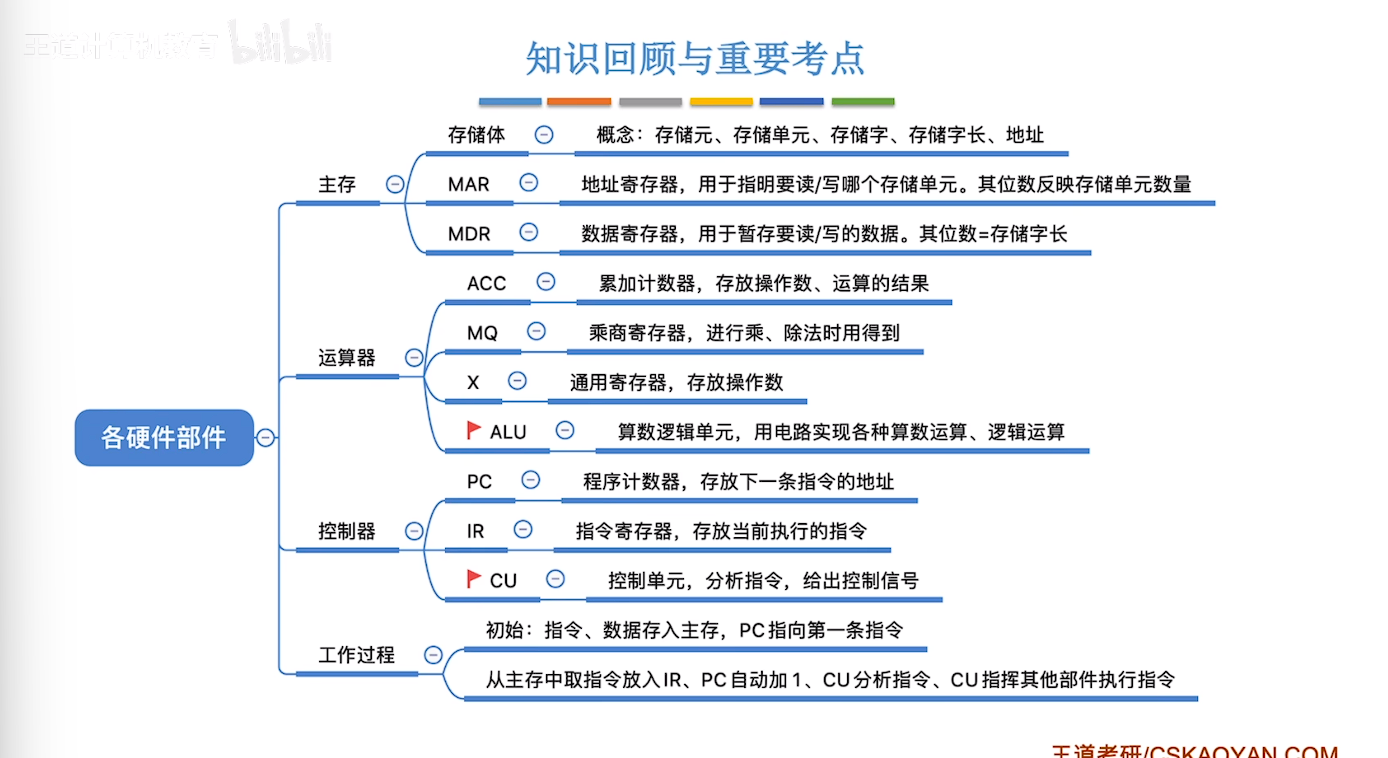

3.各个硬件的工作原理

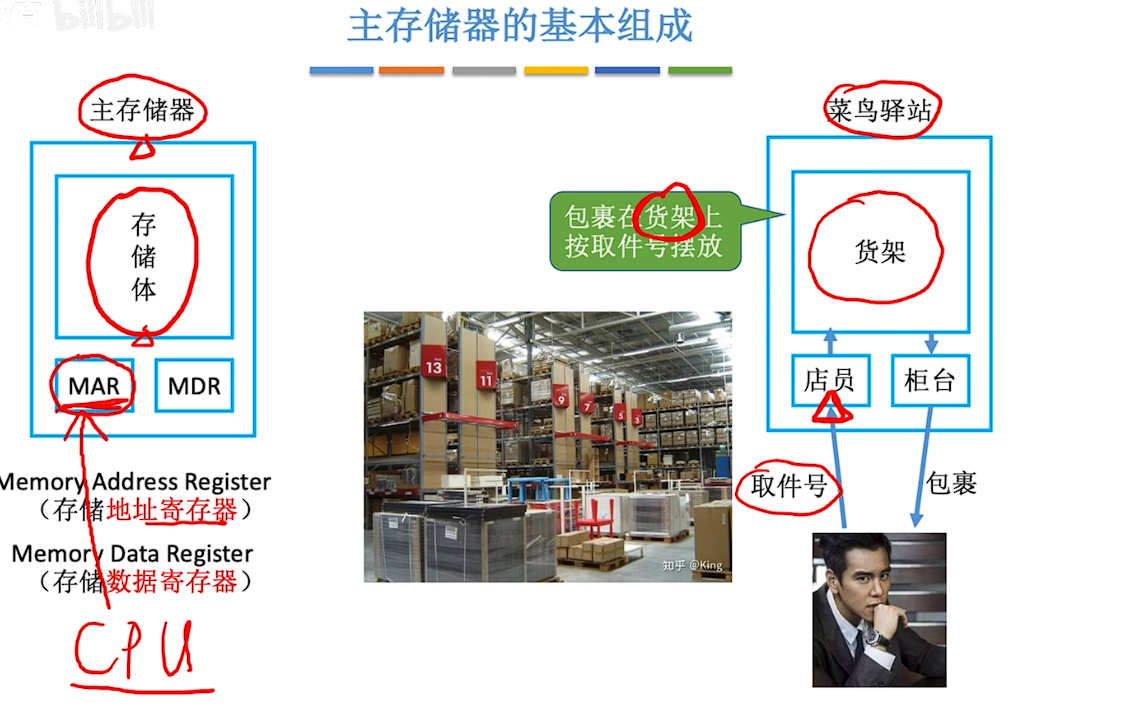

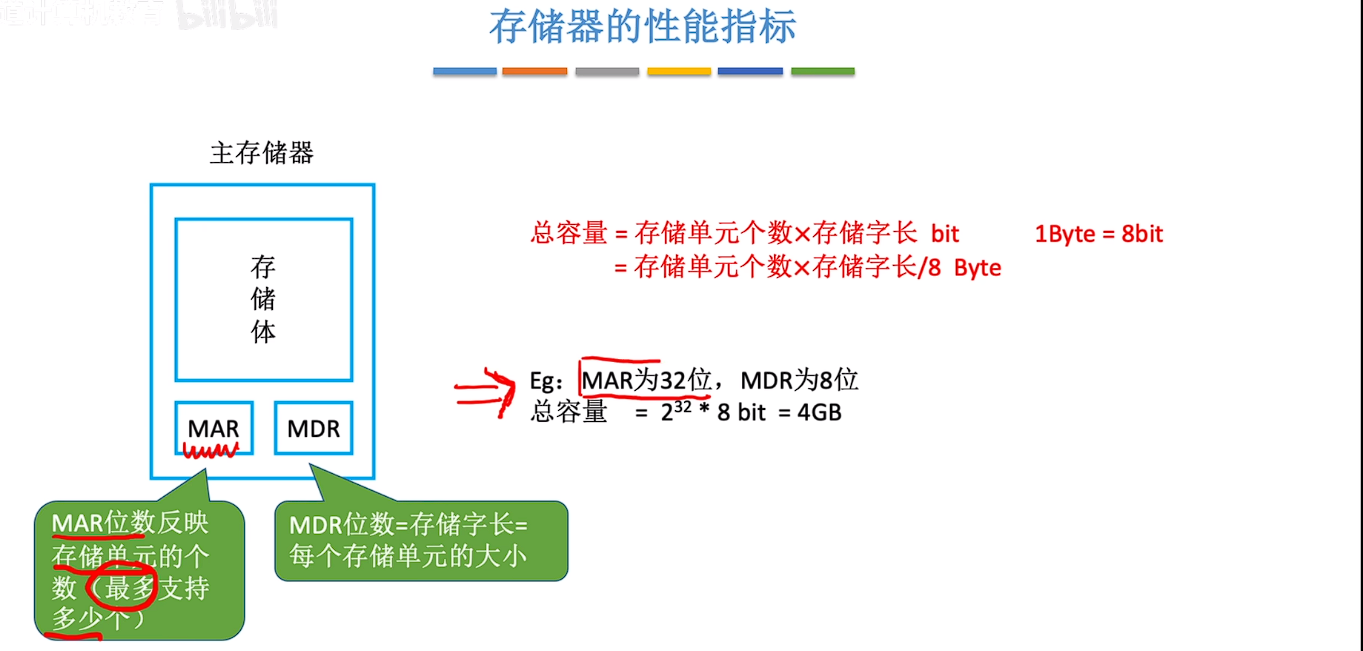

3.1主存储器的组成

存储体存放二进制信息

存储器地址寄存器(MAR)存放访存地址,经过地址译码后找到所选的存储单元。

存储器数据寄存器(MDR)用于暂存要从存储器中读或写的信息,时序控制逻辑用于产生存储器操作所需的各种时序信号。

- CPU提供了一个他想要的数据存放地址,由MAR向存储体中寻找数据,再由存储体将信息写入MDR中,最后CPU就可以通过线路从MDR中读取数据

- CPU向MAR指明他想要写入存储体中的位置(地址),数据存放在MDR中,最后CPU会通过控制总线告诉主存储器说我是想要写入数据,主存储器会根据CPU发来的信息(地址,数据和写入信号),来往存储体中写入信息

存储单元:每个存储单元存放一串二进制代码

存储字(word):存储单元中二进制代码的组合

存储字长:存储单元中二进制代码的位数

存储元:即存储二进制的电子元件,每个存储元可存1bit

3.2 运算器的组成

运算器:用于实现算术运算(如:加减乘除)、逻辑运算(如:与或非)

- ACC:累加器,用于存放操作数,或运算结果。

- MQ:乘商寄存器,在乘、除运算时,用于存放操作数或运算结果。

- X:通用的操作数寄存器,用于存放操作数

- ALU:算术逻辑单元,通过内部复杂的电路实现算数运算、逻辑运算

3.3 控制器的基本组成

- CU:控制单元,分析指令,给出控制信号

- IR:指令寄存器,存放当前执行的指令

- PC:程序计数器,存放下一条指令地址,有自动加1功能

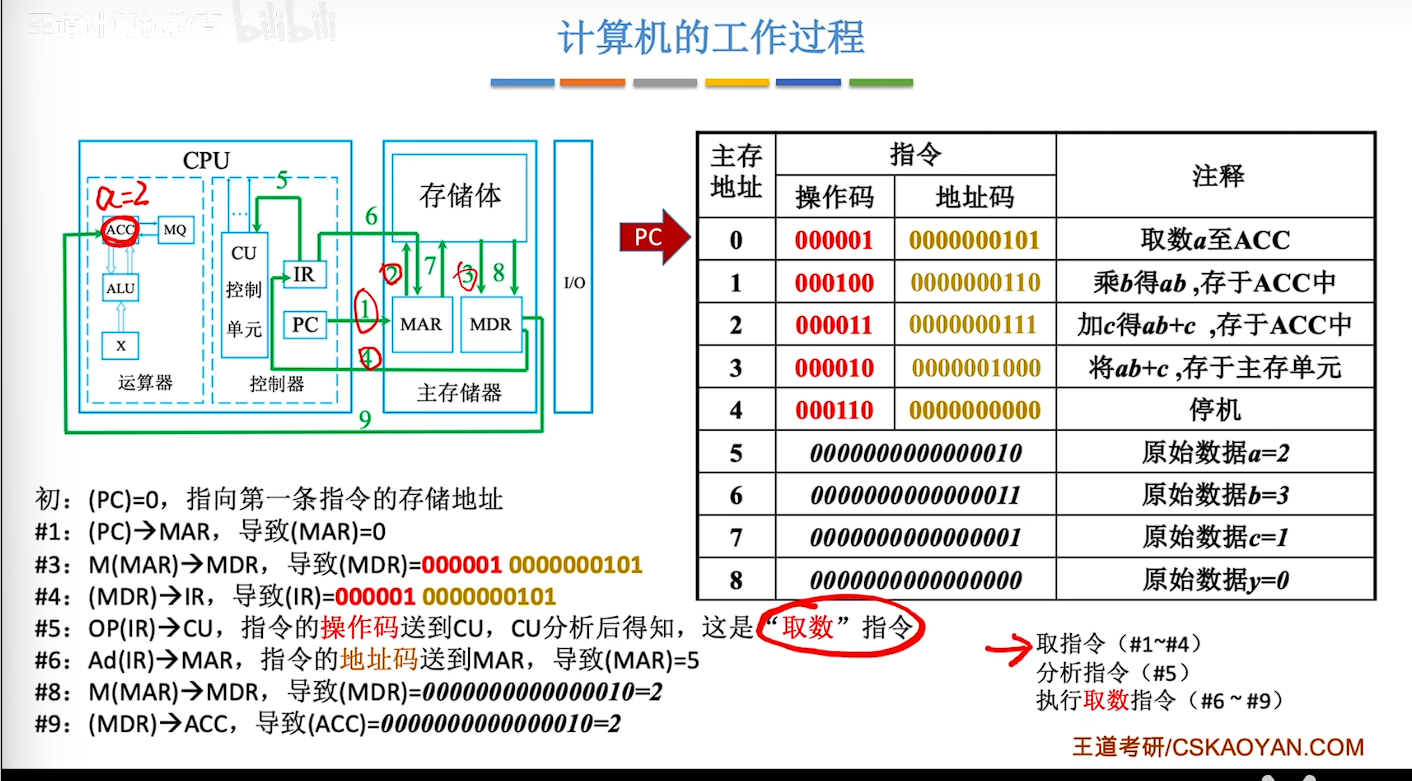

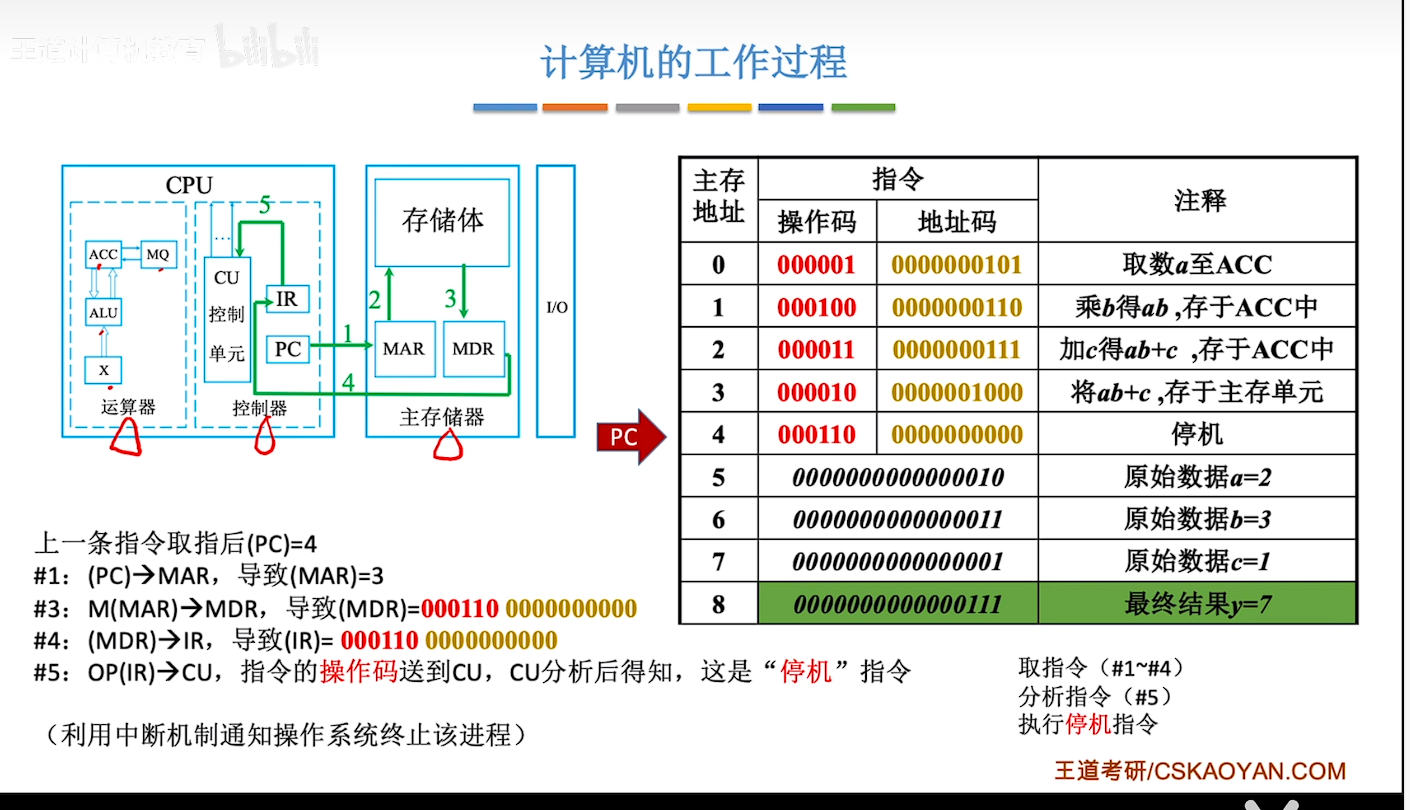

3.4 工作流程

好乱好乱好乱 ,我们现在来梳理一下

取指令(1-4)

分析指令(5)

执行取数指令(6-9)

- 程序计数器(PC)的值为 0,指向主存中第一条指令的存储地址 ,即地址 0 处的指令。

- (PC) 的值被送到主存地址寄存器(MAR),此时 (MAR)=0 ,这一步是为了告诉主存要读取哪个地址的内容。

- 根据 (MAR) 中的地址 0,从主存中读取相应的指令数据到主存数据寄存器(MDR),此时 (MDR) = 000001 0000000101,这里的数据包含操作码和地址码。

- (MDR) 中的指令数据被传送到指令寄存器(IR),(IR)=000001 0000000101,指令被暂存以便后续分析和执行。(此时PC会自动+1,由0变成1)

- 指令寄存器(IR)中的操作码部分 OP (IR) 被送到控制单元(CU) ,CU 分析操作码 000001,得知这是一条 “取数” 指令。

- 指令寄存器(IR)中的地址码部分 Ad (IR) 被送到主存地址寄存器(MAR),(MAR)=5,确定要取数的主存地址。(0000000101对应的二进制转10进制是5),而5所对应的数字就是a存放的位置

- 根据 (MAR) 中的地址 5,从主存中读取数据到主存数据寄存器(MDR),(MDR)=0000000000000010 (即十进制的 2)。

- MDR) 中的数据被传送到累加器(ACC),(ACC)=0000000000000010 ,即将数值 2 取到了 ACC 中,完成取数操作。

- 后续的指令执行过程类似,依次完成乘法、加法、存储结果和停机等操作。整个流程体现了计算机按照程序预先存储的指令,自动、有序地进行数据处理的基本原理 。

明白了吗嘿嘿

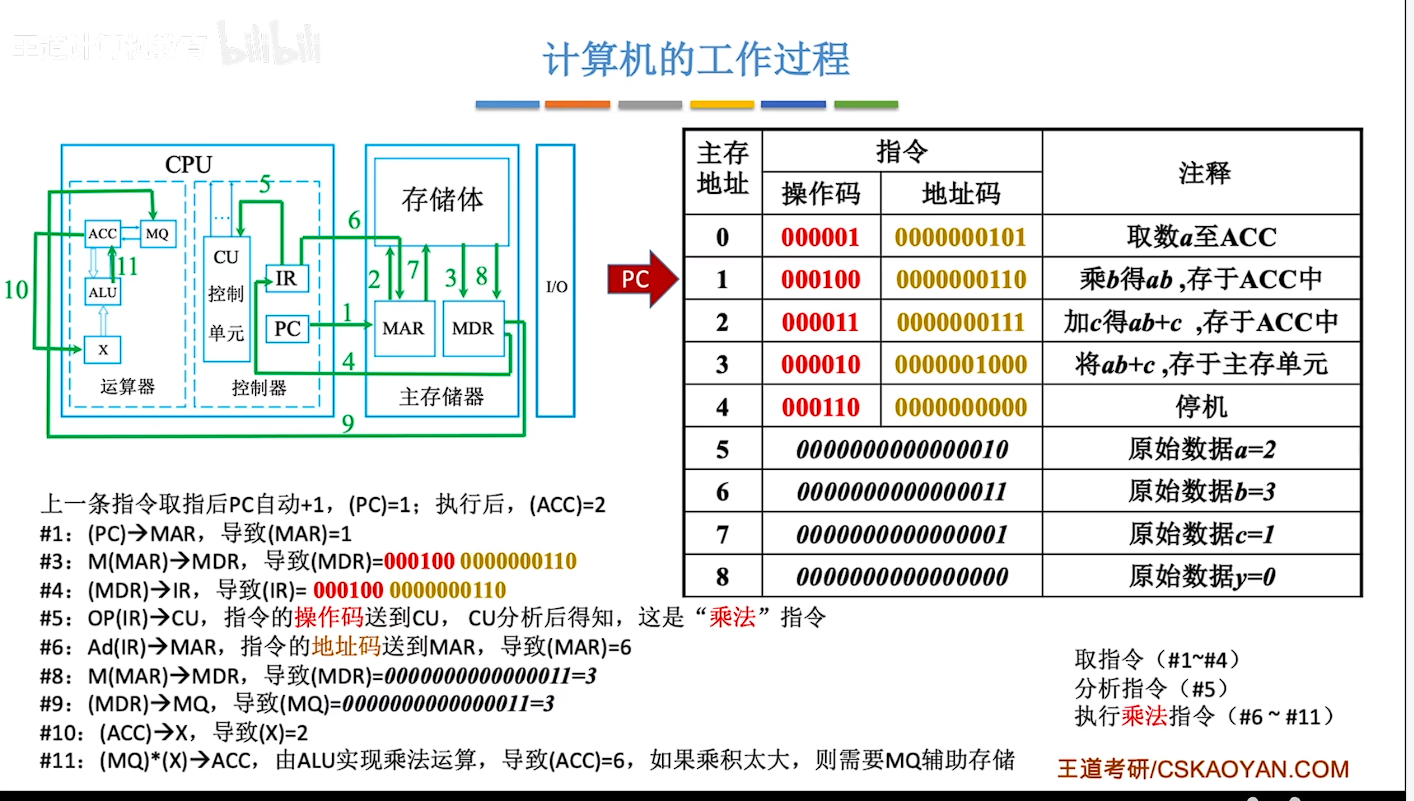

下面我们来看第二步

- 上一条指令执行后,程序计数器 (PC) 自动加 1 变为 1,指向主存地址 1 处的指令,累加器 (ACC) 中存储的值为 2。

- (PC) 的值 1 被送到主存地址寄存器 (MAR),即 (MAR)=1。

- 根据 (MAR) 中的地址 1,从主存读取指令数据到主存数据寄存器 (MDR),此时 (MDR)=000100 0000000110 。

- (MDR) 中的指令数据传送到指令寄存器 (IR),(IR)= 000100 0000000110。

- 指令寄存器 (IR) 中的操作码部分 OP (IR) 被送到控制单元 (CU),CU 分析操作码 000100,得知这是一条 “乘法” 指令。

- 指令寄存器 (IR) 中的地址码部分 Ad (IR) 被送到主存地址寄存器 (MAR),(MAR)=6。

- 根据 (MAR) 中的地址 6,从主存读取数据到主存数据寄存器 (MDR),(MDR)=0000000000000011(即十进制的 3) 。

- (MDR) 中的数据传送到乘商寄存器 (MQ),(MQ)=3。

- (ACC) 中的值 2 传送到 X 寄存器,(X)=2。

- (MQ) 和 (X) 中的值通过算术逻辑单元 (ALU) 进行乘法运算,结果存到 (ACC) 中,即 2×3 = 6,(ACC)=6 。若乘积太大,需要 MQ 辅助存储。

芜湖呜呼芜湖 我听明白了

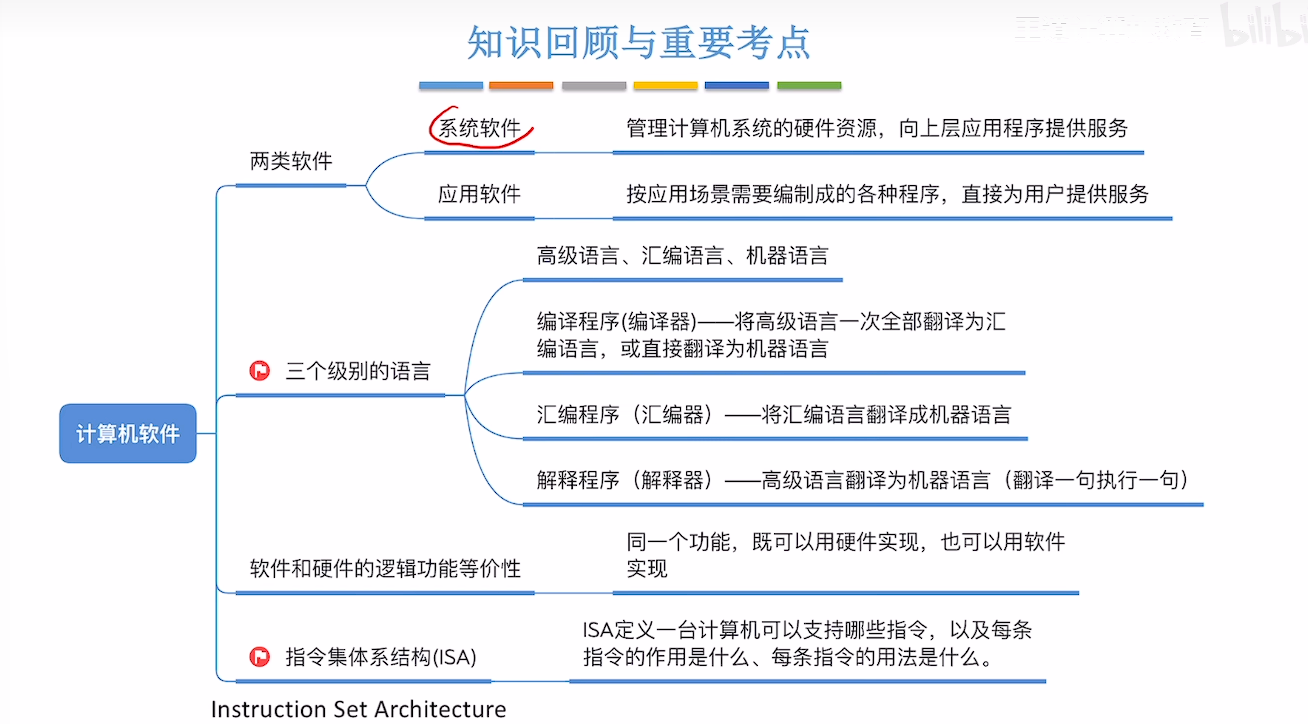

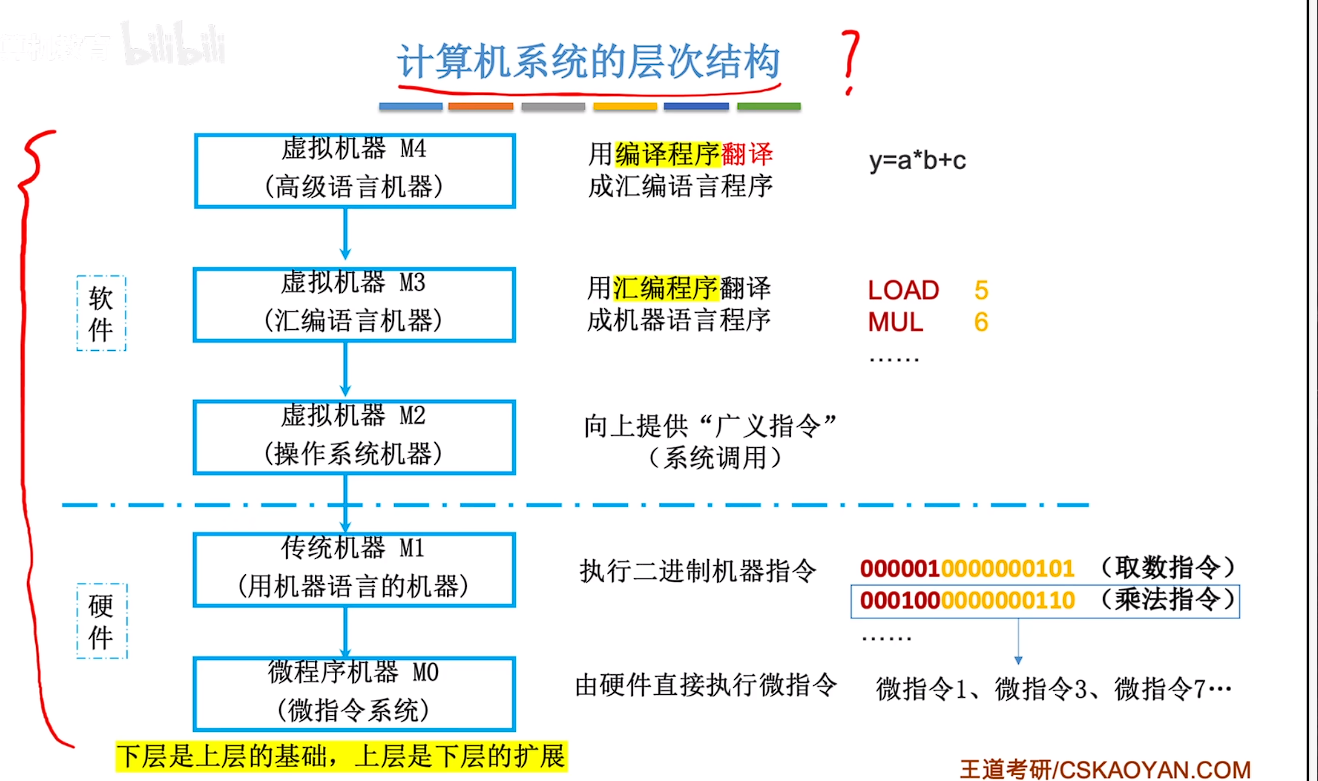

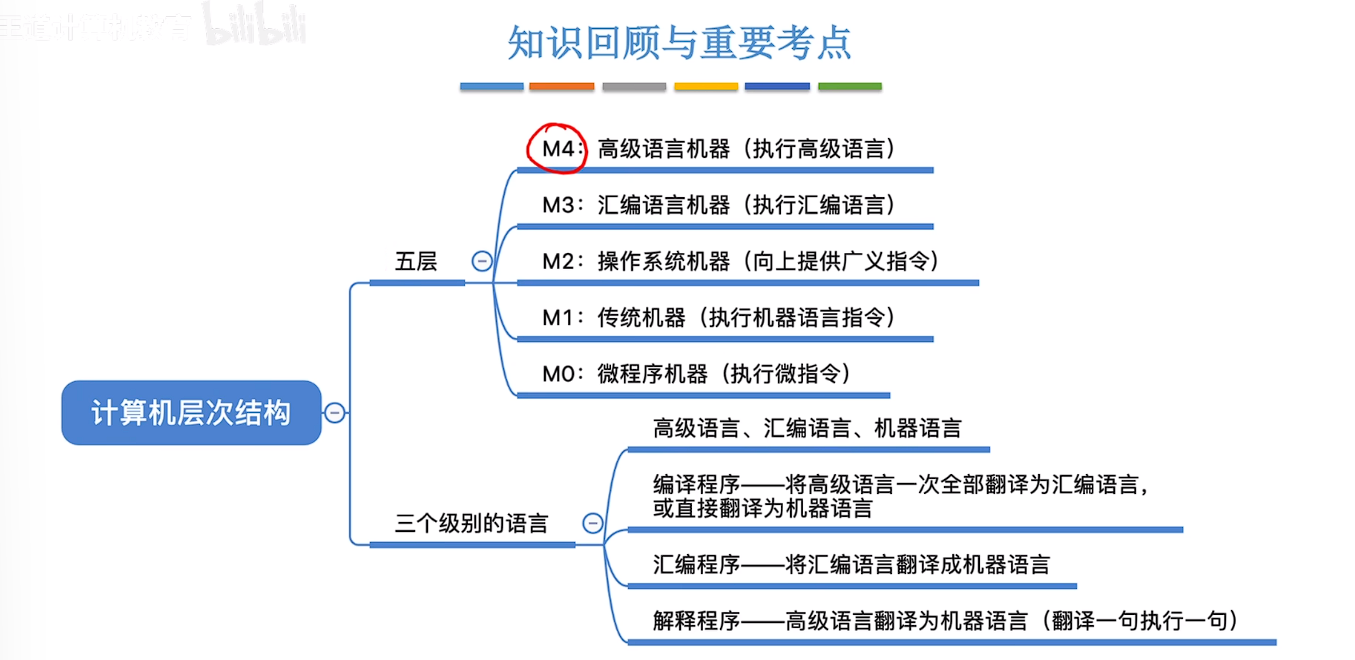

4.计算机软件

应用软件:是为了解决某个应用领域的问题而编制的程序(eg:抖音,QQ…)

系统软件:负责管理硬件资源,并向上层应用程序提供基础服务(操作系统,数据库管理系统,语言处理系统,分布式软件系统,网络软件系统,标准库程序,服务性程序)

编译程序:将高级语言编写的源程序全部语句一次全部翻译成机器语言程序,而后再执行机器语言程序(只需翻译一次)

解释程序:将源程序的一条语句翻译成对应于机器语言的语句,并立即执行。紧接着再翻译下一句(每次执行都要翻译)

软件和硬件的逻辑功能等价性:同一个功能,既可以用硬件实现(性能高成本高),也可以用软件实现(性能低成本也低)

指令集体系结构(ISA):软件和硬件之间的界面。设计计算机系统的ISA,就是要定义一台计算机可以支持哪些指令,以及每条指令的作用是什么、每条指令的用法是什么。

5. 计算机系统的层次结构

6 计算机系统的工作原理

程序执行前,先将程序第一条指令的地址存放到PC中,取指令时,将PC的内容作为地址访问主存储器。在每条指令执行过程中,都需要计算下一条将执行指令的地址,并送至PC。若当前指令为顺序型指令,则下一条指令地址为PC的内容加上当前指令的长度;若当前指令为跳转型指令,则下一条指令地址为指令中指定的目标地址。当前指令执行完后,根据PC的内容到主存储器中取出的是下一条将要执行的指令,因而计算机能周而复始地自动取出并执行一条一条的指令。

7.计算机性能指标

(二)计算机性能指标

- 吞吐最、响应时间;

- CPU 时钟周期、主频、CPI ,CPU执行时间

- MIPS, MFLOPS,GFLOPS、TFLOPS、PFLOPS、EFLOPS、ZFLOPS。;

7.1 存储器的性能指标

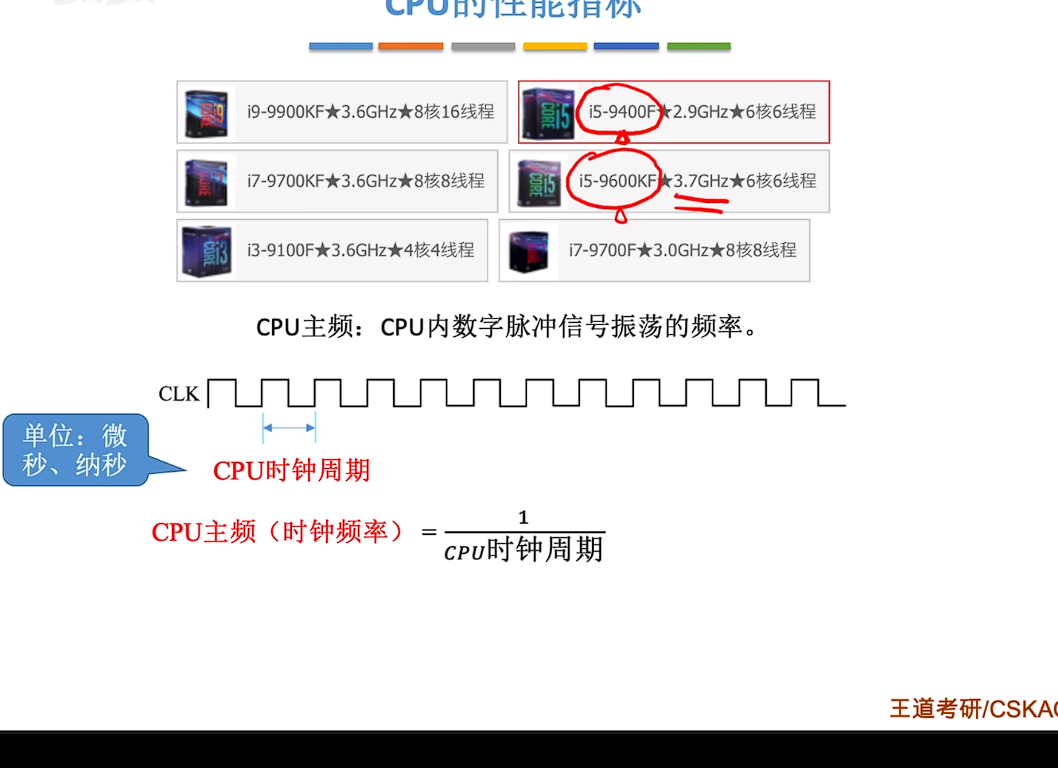

7.2 CPU 性能指标

CPU主频:CPU内数字脉冲信号振荡的频率。单位微妙,纳秒

CPU主频(时钟频率)

CPI:执行一条指令所需要的时钟周期数(不同的指令,CPI不同。甚至相同的指令,CPI也可能有变化

CPU执行时间(整个程序的耗时)=CPU时钟周期数/主频=(指令条数*CPI)/主频

IPS:每秒执行多少条指令 IPS=

一秒钟有多少个时钟周期/一条指令需要多少个时钟周期,得出一秒可以执行多少指令

eg: 一秒吃10个鸡蛋,一口可以吃3个,问一秒能吃几口

母鸡一天生产10个鸡蛋,一顿鸡蛋汤需要5个鸡蛋,问一天能吃几顿鸡蛋汤

FLOPS:每秒钟执行多少次浮点运算,单位KFLOPS,MFLOPS,GFLOPS,TFLOPS

注意:此处K,M,G,T为数量单位

K=Kilo=千=

MIPS=

- MFLOPS(每秒百万次

浮点运算) - GFLOPS(每秒十亿次

浮点运算) - TFLOPS(每秒万亿次

浮点运算) - PFLOPS(每秒千万亿

次浮点运算) - EFLOPS(每秒百京次

浮点运算) - ZFLOPS(每秒十万京

次浮点运算)

7.3 系统整体的性能指标

数据通路带宽:数据总线一次所能并行传送信息的位数(各硬件部件通过数据总线传输数据)

吞吐量:指系统在单位时间内处理请求的数量。

它取决于信息能多快地输入内存,CPU能多快地取指令,数据能多快地从内存取出或存入,以及所得结果能多快地从内存送给一台外部设备。这些步骤中的每一步都关系到主存,因此,系统吞吐量主要取决于主存的存取周期。

响应时间: 指从用户向计算机发送一个请求,到系统对该请求做出响应并获得它所需要的结果的等待时间。

二、数据的表示和运算

(一)数制与编码

进位计数制及其数据之间的相互转换

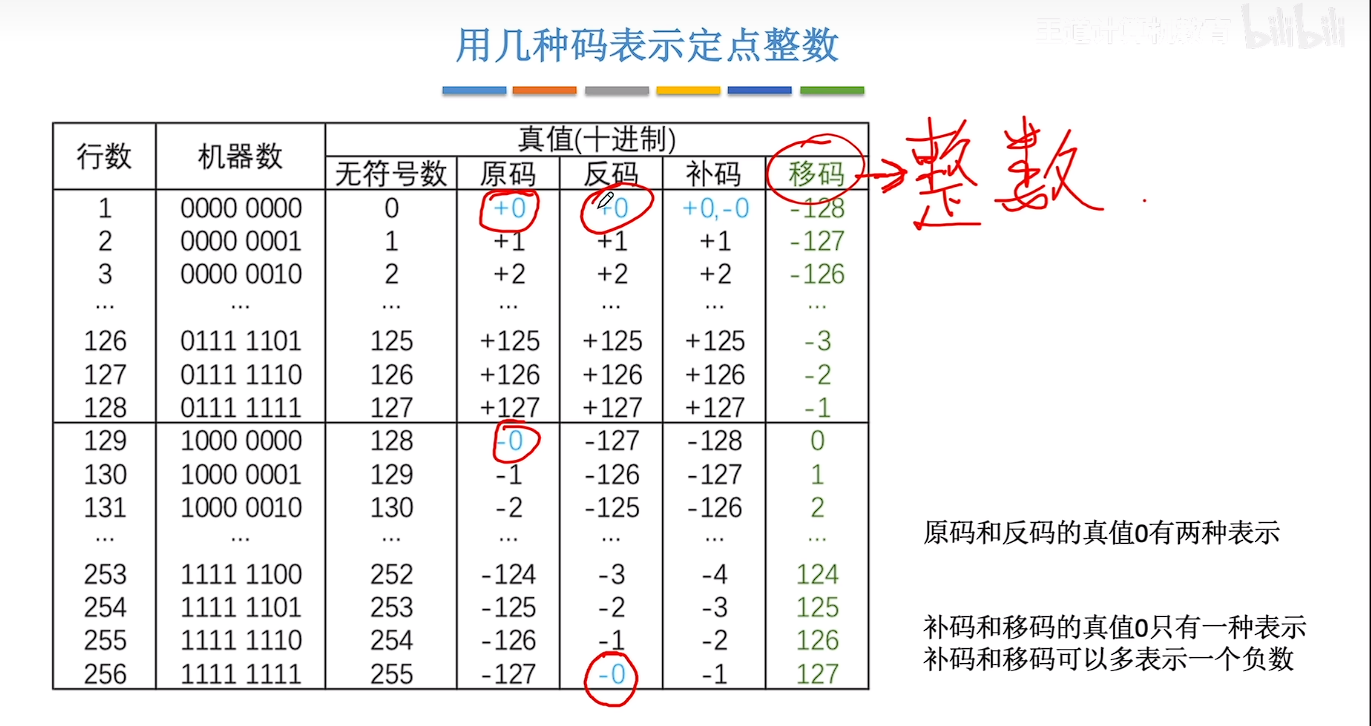

2. 定点数的编码表示

(二)运算方法和运算电路

- 1 基本运算部件: 加法器,算术逻辑部件(ALU)

加 / 减运算: 补码加 / 减运算器,标志位的生成。

3 乘 / 除运算: 乘 / 除法运算的基本原理,乘法电路和除法电路的基本结构。

(三)整数的表示和运算

1 无符号整数的表示和运算

2. 带符号整数的表示和运算

(四)浮点数的表示和运算

- 1. 浮点数的表示: IEEE 754 标准

- 2. 浮点数的加 / 减运算

1.进制转换

这我会,不写了

2.定点数的表示

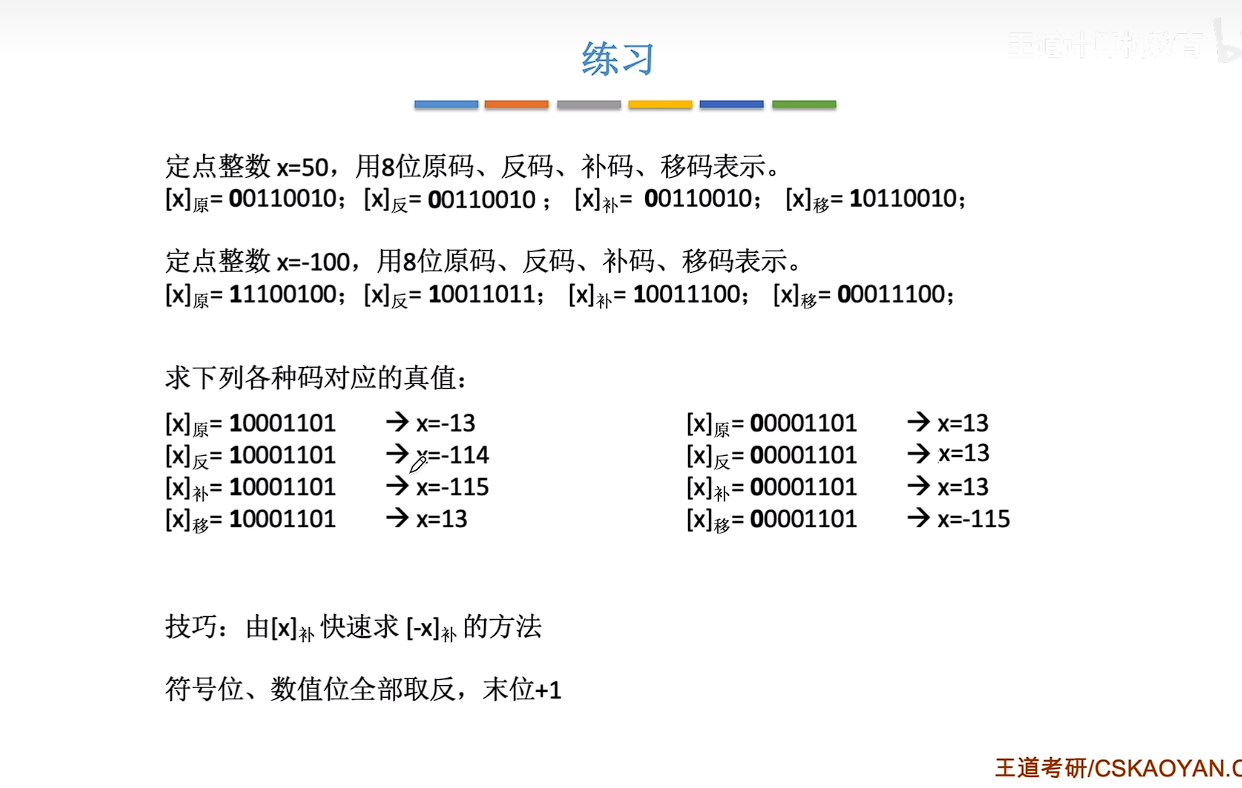

注:可用原码、反码、补码三种方式来表示定点整数和定点小数。还可用移码表示定点整数。

2.1 原码

原码:用尾数表示真值的绝对值,符号位“0/1”对应“正/负”

2.2 反码

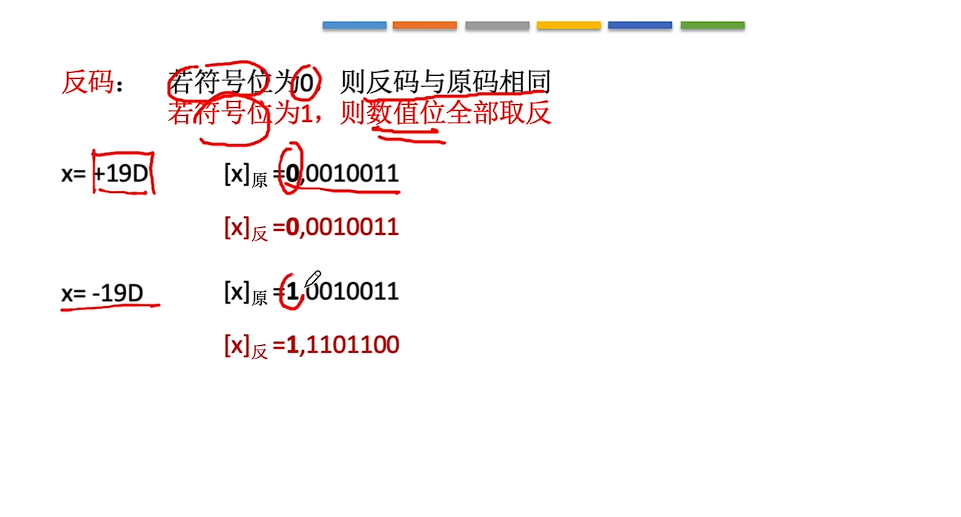

反码:若符号位为0,则反码与原码相同

若符号位为1,则数值位全部取反

2.3 补码

补码:正数的补码=原码

(负数的补码=反码末位+1(要考虑进位)

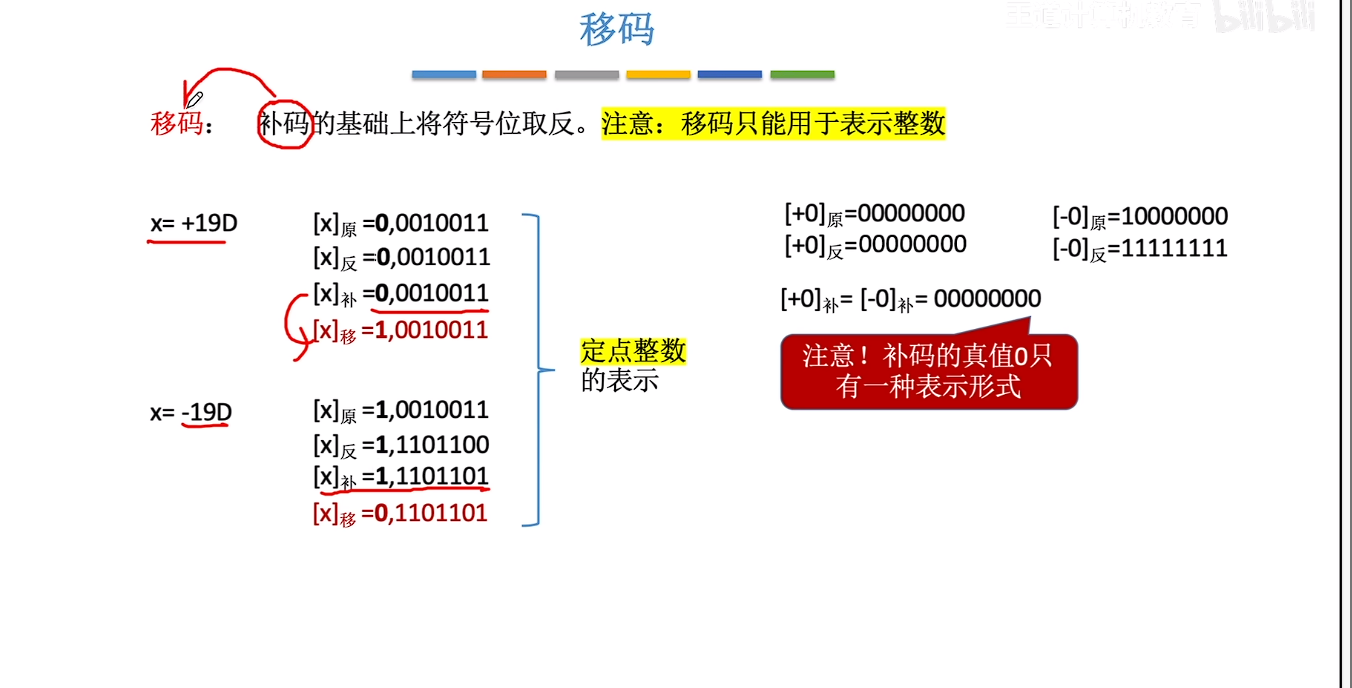

2.4 移码

移码:补码的基础上将符易位取反。注意:移码只能用于表示整数